# **AES IMPLEMENTATION FOR INTERNET-OF-THINGS DEVICES**

# S.Indarjeet Singh

Professor, Department of Electronics and Communication Engineering, Sridevi Women's Engineering College, India, Hyderabad, drindar2020@gmail.com

## B. Vaishnavi

U.G Student, Department of Electronics and Communication Engineering, Sridevi Women's Engineering College, Hyderabad, India, bonagirivaishnavi9393@gmail.com

# G. Chaturya

U.G Student, Department of Electronics and Communication Engineering, Sridevi Women's Engineering College, Hyderabad, India, chaturya0301@gmail.com

## T. Meghana

U.G Student, Department of Electronics and Communication Engineering, Sridevi Women's Engineering College, Hyderabad, India, meghanareddy752@gmail.com

## Abstract

Because of the quickly developing number of associated small gadgets to the Internet of Things (IoT), giving start to finish security is fundamental. In this way, it is crucial for plan the cryptosystem in light of the necessity of asset compelled IoT gadgets. This article presents a lightweight high level encryption standard (AES), a high-secure symmetric cryptography calculation, execution on field-programmable door cluster (FPGA) and 65-nm innovation for asset compelled IoT gadgets. The proposed design incorporates 8-digit datapath and five primary blocks. We plan two determined register banks, Key- Register and State-Register, for putting away the plain text, keys, and middle information. To diminish the region, Shift-Rows is inserted inside the State-Register. To adjust the Mix-Column to 8-bit datapath, we plan an advanced 8-bit block for Mix- Columns with four interior registers, which acknowledge 8-bit and send back 8-bit. Likewise, a common streamlined Sub- Bytes is utilized for the key extension stage and encryption stage. To upgrade Sub-Bytes, we consolidate and work on certain pieces of the Sub-Bytes. To decrease power utilization, we apply the clock gating method to the plan. Application explicit coordinated circuit (ASIC) execution results show a separate improvement nearby over the past comparable works from 35% to 2.4%. In light of the outcomes, the proposed plan is a reasonable cryptosystem for little IoT gadgets.

**Keywords:** Advanced Encryption Standard (AES) algorithm, clock gating, hardware implementation, Internet-of-things (IoT), lightweight cryptography.

## 1. Introduction

The "Web of Things" (IoT) is a huge organization of interconnected little gadgets that convey information to and fro. An e- wellbeing or public transportation framework could profit from

this data; these little gadgets could be important for an innovative organization that incorporates sensor innovation, correspondence innovation, and information handling. As the quantity of associated gadgets has been dramatically expanded, giving security to all the sent data in many situations is definitely not a simple errand. The vast majority of the end-hub little gadgets miss the mark on assets expected to perform cryptography. Because of a quickly developing IoT climate, planning minimal expense cryptography design is a significant exploration region. For battery-controlled IoT end-hub gadgets, lightweight cryptographic plans are especially appealing. It is one of the most solid symmetric cryptography calculations that are generally utilized in a large number, like the Internet of Things (IoT) and Lora Wan, as well as in other Internet conventions. AES gives a few degrees of safety in light of the length of the key. In light of the AES calculation with a 256-digit key is secure sufficient in the quantum time, and that implies that this calculation can give the security necessity of various degrees of IoT applications and conventions. With regards to executing AES, programming execution has various disadvantages, including a high deferral for handling data along with consuming more power.

Superior execution applications and asset compelled gadgets have seen a flood in the utilization of equipment executions. With 8-, 16-, and 32-bit datapaths, the AES executions for asset limited gadgets have a low throughput. Datapath engineering for asset compelled gadgets or versatile SoCs is proposed in this work. 8-digit datapath utilizes less inside wires than 32-bit datapath. We attempt to diminish the quantity of blocks, utilize the low region plan, and attempt to blend capacities to lessen the size of the plan. For putting away keys and plain text, as well as middle results, our engineering integrates two explicit register banks in light of shift-register memory: State-Register and Key-Register. Both of these registers have a critical impact in the vital extension and encryption processes, separately. FPGA and ASIC 65-nm innovation are utilized to carry out the recommended engineering. The ASIC execution of our proposed engineering is proper for cryptosystems in asset obliged IoT gadgets since it depends on NIST lightweight cryptography. Equipment execution gives off an impression of being better than earlier endeavors. For the 65-nm innovation, our proposed plan works on the area and region postpone item (ADP) for chip plan by 2.4 percent. The center region with power rings, then again, works on by 22.1 percent. A lightweight AES design for asset obliged IoT gadgets is the main commitment of our work. Execution procedures and block plans that assist us with meeting this goal incorporate the accompanying.

1) The Shift-Rows are integrated into the State-Register to improve on the necessary rationale.

2) We upgrade Sub-Bytes block and offer it with key extension stage and encryption stage, which brings about 15.5% region decrease.

3) Although Mix-Columns for executing requires 32 digits simultaneously, we plan an improved 8-bit block for Mix-Columns with 8-bit info and result that is based on the design of 8-cycle datapath, which is trailed by Add-Round-Key. In this manner, the outcomes ship off Add-Round-Key byte-by-byte. In contrast with 32-digit Mix-columns, it isn't important to store the outcomes in the registers or increment the datapath for Key-Register to 32-bit.

4) To diminish the power utilization of the design, the clock gating procedure is applied in various pieces of the plan, which prompts decrease the power utilization by 18.9% on 65-nm innovation. The remainder of this article is coordinated as follows. This paper presents the foundation of AES calculation; the proposed 8-bit datapath AES engineering and its blocks are introduced in this undertaking; the execution results, examination, and correlation with other comparative works; finally, the work is finished up.

# 2. Literature Review

A. "AES datapath optimization strategies for low-power low-energy multisecuritylevel Internet-of-Things applications,"

Associated gadgets are definitely standing out a result of the absence of safety components in current Internet-ofThing (IoT) items. The security can be improved by involving normalized and demonstrated secure block figures as cutting edge encryption standard (AES) for information encryption and confirmation. Be that as it may, these security capacities take a lot of handling endlessly power/energy utilization. In this paper, we present our equipment streamlining procedures for AES for rapid ultralow-power ultralow-energy IoT applications with various degrees of safety. Our plan upholds numerous security levels through various key sizes, power and energy streamlining for both datapath and key development. The assessed power results show that our execution might accomplish an energy for each piece practically identical with the lightweight normalized calculation PRESENT of under 1 pJ/b at 10 MHz at 0.6 V with throughput of 28 Mb/s in ST FDSOI 28-nm innovation. Concerning security assessment, our proposed datapath, 32-b key out of 128 b can't be uncovered by connection power examination assault utilizing under 20 000 follows.

# B. "Design of AES S-Box using combinational logic optimization"

High level Encryption Standard (AES) is quite possibly the most widely recognized symmetric encryption calculation. The equipment intricacy in AES is overwhelmed by AES replacement box (S-box) which is viewed as one of the most muddled and expensive pieces of the framework since it is the main non-direct construction. The proposed work utilizes a combinational rationale plan of S-Box carried out in Vertex II FPGA chip. The design utilizes a Boolean rearrangements of reality table of the rationale work fully intent on diminishing the deferral. The S-Box is planned utilizing essential entryways, for example, AND door, NOT door, OR door and multiplexer. Hypothetically, the plan diminishes the general postponement and productively for applications with fast execution. This approach is reasonable for FPGA execution in term of entryway region. The equipment, all out region and postponement are introduced.

# C. "New Area Record for the AES Combined S-box/Inverse S-box"

The AES joined S-box/converse S-box is a solitary development that is divided among the encryption and unscrambling information ways of the AES. The presently most minimized execution of the AES consolidated S-box/reverse S-box is Canright's plan, presented back in

2005. From that point forward, the exploration local area has presented a few improvements over the S-box just, but the consolidated Sbox/converse S-box got little consideration. In this paper, we propose another AES consolidated S-box/backwards S-box plan that is both more modest and quicker than Canright's plan. We accomplish this objective by proposing to utilize new pinnacle field and upgrading every single block inside the joined engineering for this field. Our intricacy examination and ASIC execution brings about the CMOS STM 65nm and Nand Gate 15nm advances show that our plan beats the partners concerning region and speed.

## 3. Finding

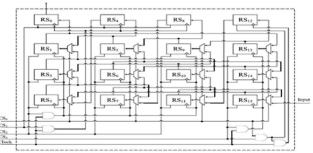

The proposed 8-bit datapath nano-AES architecture is explained here. Fig 4.1 depicts the architecture we've come up with. There are two register banks called Key-Register and State-Register that store keys and plain text and also operate as temporary registers for storing intermediate results, as well as an RCON block and a control unit in the system's design. Bypassing superfluous processes is another goal of the Mix-Columns and Sub-Bytes circuit. The design contains two feedback channels that store intermediate results into register banks during key expansion and key return . The other feedback path is used for encryption. Figure depicts the overall layout of our State-Register concept. There are sixteen 8-bit registers, each with eight flip-flops, in the State-Register.

Fig. Architecture of the proposed nano-AES design.

Using a shift-register memory structure, the State-Register receives one 8-bit input from the design and one 8-bit output if necessary. Shift-Rows are not designed as a separate block in order to save space. Neither Shift-Rows nor Sub-Bytes affect the final results because they are applied to each byte of the input. Following the Shift-Rows function, we applied the final results to the State-Register. Shift-Rows are one of the functions of the State-Register. Multiplexers are required to select from two inputs in each register of the State-Register. Encryption takes place in a register, which gets the data from the previous register.

Fig. Structure of the proposed State-Register with Shift-Rows, control circuitry, and clock gating technique.

The information is then shipped off the following register, where it is unscrambled. Fig. 4.2 shows the level interconnections among the registers in each line, while different has a few associations between the different State-Register units to execute Shift-Rows. Wiring shifts the lines, eliminating the thinking for the shift-columns step in view of thus. Twelve registers were expected by the Shift-Row block proposed by Jarvinen et al. A devoted Shift-Rows obstruct takes a ton of room and isn't great for lightweight plan. Utilizing the Shift-Rows of in our proposed State-Register requires 150 extra clock cycles for the cryptosystem's execution and has a more modern Control-Unit to enact signals contrasted with our implanted Shift- Rows in the State-Register. The Shift-Rows configuration was taken from by Zhao et al. Three 2-1 MUXs and a 4-1 MUX were found in the Shift-Register of . Twelve 2-1 MUXs are remembered for our plan. has a modern control unit in light of the fact that each MUX and a few registers have its own control signals. Thus, the exchanging factor rises, bringing about an expansion in how much power utilized . Stage procedure on lines and sections are Shift-Rows and Mix-Columns. One section of information is expected for Mix-Columns to work. After four clock cycles, one section of the State-Register is shipped off the Mix-Columns block to store and take care of the plan information. Four clock cycles later, the discoveries are conveyed back to the register. The State-Register incorporates four control flags that can be utilized to get to the registers all through every activity (CS3, CS2, CS1, and CS0). Choosing which registers are actuated is the capacity of the initial two CSs, CS1 and CS2 separately. The AND aftereffect of CS0 and CS3 is an initiation signal for the second line of registers, and CS1 is the actuation signal for the main column of registers. Dealing with a State-Register involves five essential obligations.

1) Storing the Main Plain-Text: To store the really plain text into the State-Register, every one of the inside registers ought to be enacted; hence, all the control signs ought to be set to "1." In each clock cycle, one 8-bit information is taken care of to the plan and put away in RS15. In view of the shift-register memory and interconnection between the units, when new 8- cycle information come, the put away information are communicated from RS15 to RS0.

2) Executing Shift-Rows: As it is referenced, there are

interior convergences among registers, and Shift-Rows is finished by wiring over the inward registers and interconnection. To execute Shift-Rows, the registers in the second, third, and fourth segments of the State-Register ought to be enacted. In this manner, CS0 and CS1 ought to be "0," and CS2 and CS3 ought to be "1."

3) Feeding the plan by one 8-cycle and putting away the information simultaneously founded on shift-register memory for the main Add-Round-Key and the last round, which do exclude Mix-Columns. In this activity, every one of the inner registers ought to be actuated.

4) Feeding the plan by the saved information in the principal section of the State-Register (from RS0 to RS3) by one 8-digit, for four clock cycles, and shift the register's information to execute Mix-segments (all the control signs ought to assail to "1"). After four clock cycles, the information are shiftedin which the fourth segment is prepared to store the consequence of Mix-Columns.

5) Storing the Data That Comes From Mix-Columns just in the Last Column: As it is made

sense of in Section III-B, storing the determined aftereffects of Mix-Columns into State-Register requires four clock cycles; and information ought to be put away in the last segment of the State-Register. Subsequently, just information in the last segment are moved to store the approaching information from Mix-Columns block, and information in different sections are not transmitted. During this activity, the association of the fourth and third segments of State-Register will be cut off by deactivating the interior registers in the first, second, and third segments (CS3CS2CS1CS0 will be set to "1001"). The information development of State-Register for the Add-Round-Key and the primary round is accessible in Table I; the worth ofregisters will be rehashed for different rounds.

## **Sub-Bytes Optimization**

concerning power, region, and inertness, Sub-Bytes is the main part of the AES plan. On account of the one Sub-Byte in our plan, we had the option to diminish how much silicon we want. Both the encryption and key development stages utilize a solitary Sub-Byte. Various approaches to carrying out this block are accessible. Query tables (LUTs) and the Boolean improvement map (which utilizes a reality table to lay out an immediate connection between the Sub-Bytes boundaries) are the most direct ways of executing, however they occupy more room and are hence unsatisfactory for space-compelled gadgets.

use Decode-Switch-Encode (DSE) to carry out Sub-Bytes, which is a sensible answer for lowpower structures, despite the fact that it occupies more room. Compound field number juggling, considering present realities the most productive way to deal with execute Sub-Bytes.

At the end of Sub-Bytes, the multiplicative inverse of the f (x) is g(x), which is  $g(x) \mod(x8+x4+x3+x+1) = 1$  GF(28multiplication)'s inverse is difficult to compute, however using composite field arithmetic simplifies the process considerably." GF(28) is decomposed into its constituent fields using the composite field, and the multiplicative inverse is then determined using that result. When designing area-constrained devices, composite field arithmetic and AT of are the most efficient methods. We choose the irreducible polynomials based on earlier work.

$$\begin{array}{c} \operatorname{GF}\left(2^{2}\right) \xrightarrow{} \operatorname{GF}\left(2\right): x^{2} + x + 1 \\ \operatorname{GF}\left(\left(2^{2}\right)^{2}\right) \xrightarrow{} \operatorname{GF}\left(2^{2}\right): x^{2} + x + \varphi \\ \operatorname{GR}\left(\left(\left(2^{2}\right)^{2}\right) \xrightarrow{} \xrightarrow{} \operatorname{GF}\left(\left(2^{2}\right)^{2}\right): x^{2} + x + \lambda \end{array}\right) \end{array}$$

By mapping GF (28) to its lower field, each element "A" can be represented by Ah x + Al, where Ah is the most significant part and Al is the least significant part based on the irreducible polynomial  $x^2 + x + \lambda$ . By selecting the irreducible polyno-mial, the multiplicative inverse is calculated by

$$\begin{aligned} (\mathbf{A}_{h}\mathbf{x} + \mathbf{A}_{l})^{-1} &= \mathbf{A}_{h} \left(\mathbf{A}_{h}^{2} \lambda + \mathbf{A}_{l} \left(\mathbf{A}_{h} + \underline{\mathbf{A}_{l}}\right)\right)^{-1} \mathbf{x} \\ &+ (\mathbf{A}_{h} + \underline{\mathbf{A}_{l}})(\mathbf{A}_{h}^{2} + \mathbf{A}_{l}(\mathbf{A}_{h} + \mathbf{A}_{l}))^{-1} \end{aligned}$$

GF(28) to GF((24)2) is explained in detail . The isomorphic function, " $\delta$ ," is used to transfer from GF(28) to its composite field, and the inverse isomorphic, " $\delta$ -1," is used to transfer from composite field to its value in GF(28). " $\delta$ " is an 8 × 8 binary matrix that is calculated by the field polynomials of GF(28) and its composite fields. by selecting P(x) = x8 + x4 + x3 + x +1

ISSN: 1533 - 9211 and using the subfield of (1), the isomorphic function can be calculated as

$$\delta(x) = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 1 & 1 & 1 & 1 & 0 \\ 1 & 0 & 1 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 0 & 1 & 1 & 1 & 0 \\ 0 & 1 & 0 & 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 1 & 1 \end{bmatrix} \times \begin{bmatrix} x_7 \\ x_6 \\ x_8 \\ x_4 \\ x_3 \\ x_1 \\ x_2 \\ x_0 \end{bmatrix}$$

" which is written as

The inverse isomorphic function "," which is written as

|                    |     | - |   |   |   |   |   |        |   | -                     |   |

|--------------------|-----|---|---|---|---|---|---|--------|---|-----------------------|---|

|                    | [1  | 1 | 1 | 0 | 0 | 0 | 1 | 0      |   | X7                    | 1 |

|                    | 0   | 1 | 0 | 0 | 0 | 1 | 0 | 0      |   | <i>x</i> <sub>6</sub> |   |

|                    |     |   |   |   |   |   |   | 0      |   | x5                    |   |

| s-1(m) -           | 0   | 1 | 1 | 1 | 0 | 1 | 1 | 0<br>0 |   | X4                    |   |

| $\delta^{-1}(x) =$ | 0   | 0 | 1 | 1 | 1 | 1 | 1 | 0      | × | <i>x</i> <sub>3</sub> |   |

|                    |     |   |   |   |   |   |   | 0      |   | $x_2$                 |   |

|                    | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 0      |   | $x_1$                 |   |

|                    | 0   | 1 | 1 | 1 | 0 | 1 | 0 | 1      |   | <i>x</i> <sub>0</sub> |   |

|                    | L . |   |   |   |   |   |   | -      |   | L -                   | 1 |

is constructed by inverting the  $8 \times 8$  matrix " $\delta$ ".

After calculating the multiplication inverse followed by inverse isomorphic function ( $\delta$ -1), the AT is applied to achieve the final result. In the following equation, AT is the affine transformation, f (x) is the result from the multiplication inverse followed by inverse isomorphic function,  $\varphi$  is a con-stant number ( $\varphi$  is equal to {63}8), and g(x) is the final result of Sub-Bytes block:

The Sub-Bytes of f(x) is g(x) and is calculated by

$$g(x) = \operatorname{Sub}(f(x))$$

= (IMUL( $\delta \times f(x)$ ) ×  $\delta^{-1}$ ) × AT  $\oplus \phi$

= (IMUL( $\delta \times f(x)$ )) × ( $\delta^{-1} \times$  AT  $\oplus \phi$ )

= (IMUL( $\delta \times f(x)$ )) ×  $\gamma$ .

. Entity diagram for nano-AES is shown below

| Din(127:0) | Dout(127:0) |

|------------|-------------|

| Kin(127:0) | BSY         |

| CLK        | 0.51        |

|            |             |

|            | Kvid        |

| Krdy       |             |

| RSTn       | set         |

RTL schematic for nano-AES is shown below

Simulation results are obtained as follows

## 4. Conclusion

Consistently, an ever increasing number of devices are becoming interconnected through the Internet of Things (IoT). The security of a correspondence network couldn't possibly be more significant. IoT gadgets are regularly little and have restricted assets, making start to finish security basic. In numerous applications and organizations, AES is a profoundly solid symmetric cryptographic strategy with an elevated degree of safety. In this manner, AES is a reasonable calculation for IoT gadgets that are little and light. For IoT gadgets with restricted assets, we have fostered a lightweight AES engineering. A 8-digit datapath and two indicated register banks were integrated into the design for the capacity of plain text, keys and transitional results. Shift-Rows was run within the State Register to diminish how much rationale required. On 65-nm innovation, the plan had an upgraded Sub-Bytes imparted to encryption and key development, which decreased the space by 15.5%. Likewise, we made blend Columns, a lowregion configuration block with 8-bit information and result. With the utilization of the clock gating strategy, we had the option to bring down power utilization across a few particular plan blocks Using the Virtex-5 FPGA, we had the option to test the engineering. At long last, the 65-nm innovation was utilized to carry out and test the proposed plan. With the power rings, the chip's center region is 5448.59 m<sup>2</sup>. Without the power rings, the chip's center region is 7783.77 m2. The region and ADP for chip configuration were worked on by 2.4 percent and 71.7 percent, separately, by the proposed plan. What's more, the center region with power rings was expanded by 22.1 percent over the best comparative execution. The plan's power utilization was reenacted in an assortment of time spans. Ascertaining past works' standardized power permitted us to contrast our work with others in the field. The proposed plan had a lower power use than most of the earlier endeavors. The proposed lightweight AES configuration, as per the outcomes and the NIST report, might be conveyed by low-power gadgets and is appropriate for

asset compelled gadgets. It's notable that AES is an incredibly protected symmetric calculation. In the quantum period, the AES with a 256-cycle key length is secure. We'll be chipping away at an asset obliged IoT gadget AES with postquantum opposition later on. This essentially affects the region, power, and inactivity of a game. We'll utilize an improved plan design to eliminate power and space as an answer for these issues.

## References

[1] N. Sornin, M. Luis, T. Eirich, T. Kramp, And O.Hersent, "Lorawanspecification," Lora Alliance, Tech. Rep., Jan. 2015, Pp. 1–82.[Online]. Available: Https://Loraalliance.Org/ResourceHub/Lorawanrspecification-V10

[2] Z. Liu, K.-K. R. Choo, And J. Großschädl, "Securing Edge Devices In The Post-Quantum Internet Of Things Using Lattice-Based Cryptography,"Ieee Commun. Mag., Vol. 56, No. 2, Pp. 158–162, Feb. 2018.

[3] D.-H. Bui, D. Puschini, S. Bacles-Min, E. Beigné, And X.-T. Tran, "Aes Datapath Optimization Strategies For Low- Power Low-Energy Multisecuritylevel Internet-Of-Things Applications," Ieee Trans. Very Large Scale Integr. (Vlsi) Syst., Vol. 25, No. 12, Pp. 3281–3290, Dec. 2017.

[4] C. Patrick And P. Schaumont, "The Role Of Energy In The Lightweightcryptographic Profile," In Proc. Nist Lightweight Cryptogr. Workshop,2016, Pp. 1–16.

[5] A. Moradi, A. Poschmann, S. Ling, C. Paar, And H. Wang, "Pushing The Limits: A Very Compact And A Threshold Implementation Of Aes,"In Proc. Annu. Int. Conf. Theory Appl. Cryptograph. Techn. Tallinn, Estonia: Springer, 2011, Pp. 69–88.

[6] T. Järvinen, P. Salmela, P. Hämäläinen, And J. Takala, "Efficient Byte Permutation Realizations For Compact Aes Implementations," In Proc.13th Eur. Signal Process. Conf., 2005, Pp. 1–4.

[7] W. Zhao, Y. Ha, And M. Alioto, "Aes Architectures For Minimum-Energy Operation And Silicon Demonstration In 65 Nm With Lowest Energy Per Encryption," In Proc. Ieee Int. Symp. Circuits Syst. (Iscas), May 2015,

Pp. 2349–2352.

[8] K. Shahbazi, M. Eshghi, And R. Faghih Mirzaee, "Design And Implementation Of An Asip-Based Cryptography Processor For Aes, Idea, And Md5," Eng. Sci. Technol., Int. J., Vol. 20, No. 4, Pp. 1308–1317, Aug. 2017.

[9] L. Ali, I. Aris, F. S. Hossain, And N. Roy, "Design Of An Ultra High Speed Aes Processor For Next Generation It Security," Comput. Electr. Eng., Vol. 37, No. 6, Pp. 1160–1170, Nov. 2011.

[10] A. Soltani And S. Sharifian, "An Ultra-High Throughput And Fully Pipelined Implementation Of Aes Algorithm On Fpga," Microprocessors Microsyst., Vol. 39, No. 7, Pp. 480–493, Oct. 2015.